半導體可靠度驗證:原理、標準與 HTOL 測試解決方案

半導體可靠度基礎

可靠度的必要性:從消費性商品到任務關鍵型系統

在當代電子產業中,可靠度(Reliability)已不僅僅是一個品質指標,更是決定產品成敗、企業信譽乃至使用者安全的基石;可靠度的核心定義為:一個產品在規定的時間內,於特定的使用環境條件下,能夠成功執行其預定功能的機率,此概念的量化與驗證,構成了整個可靠度工程的核心。

隨著科技的演進,對可靠度的要求正以前所未有的速度急劇攀升。此趨勢主要由以下幾個關鍵因素驅動:

- 製程微縮與複雜度提升:

隨著半導體製程節點進入奈米等級,元件尺寸不斷縮小,而單一晶片上整合的電晶體數量卻呈指數級增長,系統單晶片(SoC)、人工智慧(AI)加速器等高複雜度元件,其內部潛在的失效點也隨之增多,任何微小的製程瑕疵或設計缺陷都可能被放大,進而影響整個系統的穩定性。

- 新興應用領域的嚴苛要求:

電子產品的應用範疇已從傳統的消費性電子,大規模擴展至對安全性與穩定性有著零容忍要求的領域,例如,在汽車電子領域,AEC-Q100等規範已成為產業標準,要求元件必須在極端的溫度與應力環境下長時間穩定運作,同樣地,在航空太空、醫療植入設備以及關鍵基礎設施等任務關鍵型(Mission-Critical)應用中,元件的失效可能導致災難性後果,因此其可靠度標準遠超一般商業產品。

- 市場競爭與品牌價值:

在競爭激烈的市場中,產品的可靠度直接關係到使用者體驗與品牌形象,一次大規模的產品召回或現場失效事件,不僅會帶來巨大的財務損失,更會嚴重侵蝕消費者對品牌的信任;因此,提供具有可驗證、可量化可靠度數據的產品,已成為半導體供應商贏得客戶信賴與維持市場競爭力的核心要素。

總而言之,可靠度驗證已從過去的生產後端品質控制環節,演變為貫穿產品整個生命週期的策略性活動,從設計、製造、封裝到最終應用的每一個階段,都必須將可靠度作為核心考量。

量化可靠度:失效的語言

為了將抽象的「可靠」概念轉化為可測量、可比較的工程數據,業界建立了一套標準化的數學語言來描述與預測產品的失效行為,這些指標是半導體供應商與系統製造商之間溝通品質與壽命的共同基礎。

- 可靠度函數 (R(t)):

這是描述產品在時間 t 之前未發生失效的機率。對於半導體元件在其主要使用壽命期間,其失效行為通常被假設遵循指數分佈。在此假設下,可靠度函數可表示為:

R(t) = e-λt其中,λ 是失效率,一個關鍵的衡量參數。

- 失效率 (λ):

失效率定義為單位時間內發生失效的產品比例。其常用單位為「%/1000小時」,意指每運行1000小時的元件中,出現失效的百分比,這個指標直觀地反映了產品的失效傾向。

- FIT (Failures In Time):

在對可靠度要求極高的應用中,失效率的數值往往非常小。為了更精確地表達這種極低的失效率,業界引入了FIT作為標準單位;1 FIT的定義為「每十億 (109) 個元件小時內發生一次失效」,其換算關係為:1 FIT = 10-9 failures/hour = 0.0001%/1000 hours,FIT是汽車、通訊和航太等領域中,規格書與合約裡最常見的可靠度指標。

- MTTF (Mean Time To Failure,平均失效時間):

對於像積體電路(IC)這樣不可修復的元件,MTTF是衡量其可靠度的另一個重要指標。它表示產品從開始使用到發生失效的平均時間,在失效率 λ 為一常數的指數分佈假設下,MTTF是失效率的倒數:

μ = MTTF = 1/λMTTF提供了對產品預期壽命的直觀估計。

這些指標並非僅是學術上的定義,它們在商業實踐中扮演著至關重要的角色,例如,一家汽車製造商在採購用於引擎控制單元(ECU)的晶片時,會在採購合約中明確規定其可接受的最大FIT率;半導體供應商必須透過一系列嚴格的可靠度測試(如後續將詳述的HTOL測試),來驗證其產品能夠滿足此規格;因此,準確計算、預測並透過協力廠商實驗室驗證這些可靠度指標的能力,已成為半導體公司不可或缺的核心競爭力。

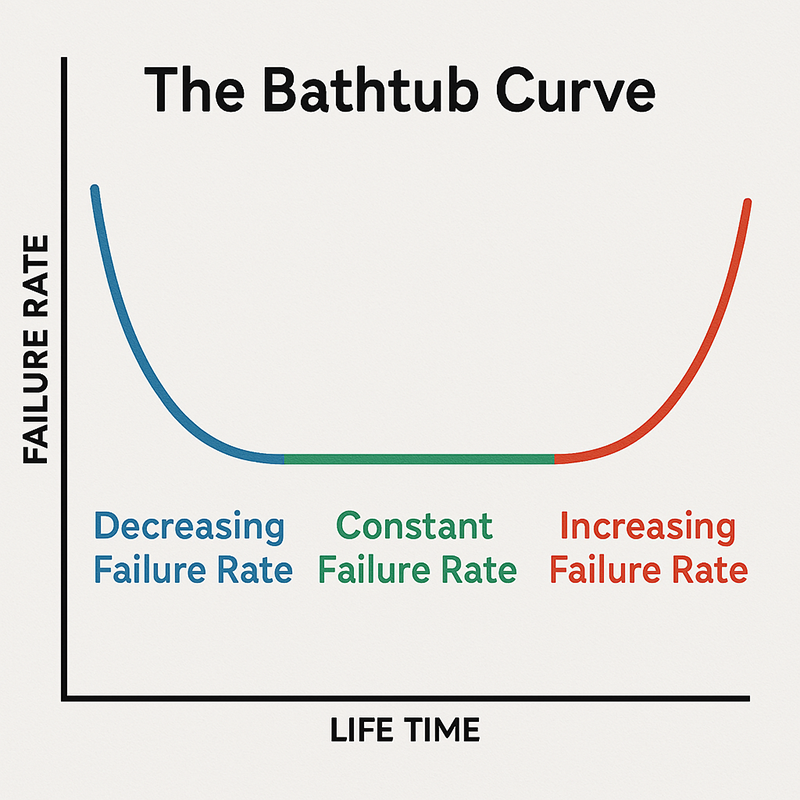

浴盆曲線:產品的生命故事

半導體產品在其整個生命週期中的失效率並非一成不變,而是呈現出一個典型的、形似浴盆的變化趨勢,這便是著名的「浴盆曲線」(Bathtub Curve),該曲線清晰地揭示了產品在不同生命階段的失效特性,並為可靠度測試策略的制定提供了根本性的指導框架。

The Bathtub Curve

浴盆曲線主要分為三個不同的時期:

- 第一階段:初期失效期(Infant Mortality / Early Life Failure)

此階段的特點是失效率由一個較高的水準迅速下降。此時發生的失效,其根本原因通常源於設計或製造過程中的潛在缺陷,例如製程變異、材料污染、微觀結構瑕疵等;這些「體質孱弱」的產品在投入使用初期便會迅速失效。

- 第二階段:隨機失效期(Random Failure / Useful Life)

在淘汰了初期失效的產品後,產品進入其主要的使用壽命期。此階段的失效率非常低,且基本保持為一個常數;此時的失效被認為是隨機發生的,可能由外部應力(如電氣過應力EOS)或一些無法預測的偶然因素觸發,可靠度工程的主要目標之一,就是盡可能地延長這一時期的長度,並降低此階段的失效率(即FIT率)。

- 第三階段:耗損失效期(Wear-out Failure)

當產品接近其物理壽命極限時,由於材料老化、結構疲勞等耗損機制開始顯現,其失效率會迅速攀升;這些失效是可預期的,由元件內在的物理或化學退化過程所主導,例如電子遷移、氧化層崩潰等。

浴盆曲線不僅僅是對產品生命歷程的描述,它更是整個可靠度驗證體系的戰略藍圖;所有看似繁雜的可靠度測試項目,實際上都是針對浴盆曲線不同階段所設計的目標性行動,例如,「早期壽命失效(Early Life Failure Rate, ELFR)」測試或生產中的「老化篩選(Burn-in)」,其目的就是模擬產品的初期使用,以加速篩選出那些存在潛在缺陷的「早夭」產品,從而避免它們流入客戶手中,這是在管理曲線的第一階段;而「高溫操作壽命(High Temperature Operating Life, HTOL)」測試,其核心目標則是透過加速耗損機制,來預測隨機失效期的長度(即產品的有效壽命),並確保耗損期的起點遠遠晚於產品規格書中所承諾的壽命,這是在管理曲線的第二和第三階段的邊界;因此,一個全面的可靠度計畫,其本質就是一場精心策劃的戰役:在產品出廠前,主動清除第一階段的威脅;並透過科學的預測,確保產品在整個預期壽命內,能安全地停留在第二階段的平穩期。

國際可靠度標準與關鍵測試方法概覽

為了確保全球電子產業在可靠度評估上有一致的標準和可比較的結果,多個國際標準化組織應運而生;它們制定的規範不僅定義了測試方法,更建立了整個產業鏈從元件製造商到終端產品客戶之間的信任基礎。

標準化組織的角色:JEDEC、AEC 與 MIL-STD

- JEDEC (Joint Electron Device Engineering Council,固態技術協會):

作為半導體工程領域最重要和最基礎的標準化組織,JEDEC的標準涵蓋了從設計、製造、封裝到測試的整個產業生態系;其發布的JESD系列標準是全球商用和工業級電子元件可靠度驗證的黃金標準,其中,JESD47規範了積體電路的整體認證流程,而JESD22系列則詳細定義了各種環境與電氣應力測試的具體方法,例如JESD22-A108 (HTOL)、JESD22-A104 (溫度循環) 等。

- AEC (Automotive Electronics Council,汽車電子協會):

由克萊斯勒、福特和通用汽車等公司發起成立,目的為供應汽車產業的電子元件建立一套通用的品質與可靠度標準;其最著名的規範AEC-Q100,是針對積體電路的壓力測試認證標準。相較於JEDEC,AEC-Q100通常對元件的工作溫度範圍、測試時長和可接受的失效率有著更為嚴苛的要求,以應對汽車內部複雜且惡劣的運行環境。

- MIL-STD (Military Standard,美國軍用標準):

在JEDEC和AEC之前,軍用標準是推動電子元件可靠度發展的先驅;MIL-STD-883等規範為國防和航空太空應用設定了極高的可靠度門檻,許多現行的商規測試方法,其雛形都源自於軍規要求;儘管在商業應用中已逐漸被JEDEC和AEC標準取代,但在高可靠性領域,軍規標準依然具有重要的參考價值。

環境壓力測試:模擬自然元素的挑戰

環境壓力測試目的在模擬元件在儲存、運輸及實際工作中可能遭遇的各種惡劣環境,以加速暴露其在封裝和材料方面的潛在弱點。

溫濕度壓力:腐蝕的威脅

濕氣是影響非氣密性封裝元件可靠度的主要殺手之一;濕氣會沿著封裝材料(如環氧樹脂)與導線架之間的介面,或透過材料本身的微小孔隙滲透至晶片表面,進而引發多種失效機制。

- 溫濕度偏壓測試 (THB, Temperature-Humidity-Bias):

依據JESD22-A101標準,THB測試重點在評估元件在長期高溫、高濕及電壓偏壓共同作用下的可靠性,其典型的測試條件為85°C溫度、85%相對濕度(因此也常被稱為「雙85測試」),並在元件的引腳上施加持續的電壓偏置,測試時間長達1000小時;此測試主要用於加速伽凡尼腐蝕(電化學腐蝕)、化學腐蝕以及金屬離子遷移等反應速率相對較慢的失效機制。

- 高加速應力測試 (HAST, Highly Accelerated Stress Test):

依據JESD22-A110標準,HAST可視為THB的加速版本;它利用更高的溫度(如110°C或130°C)和高於大氣壓的壓力(如1.2至2.3 atm),來極大地提升水蒸氣的分壓,從而顯著加速濕氣侵入封裝體的速度;相較於需要1000小時的THB測試,HAST通常只需96至264小時即可達到相似的加速效果,極大地縮短了驗證週期。

- 無偏壓高加速應力測試 / 壓力鍋測試 (uHAST / PCT):

依據JESD22-A102標準,此測試採用與HAST類似的高溫、高濕、高壓條件,但不施加電壓偏壓,其測試目的純粹是評估封裝結構本身的完整性,以及其抵抗濕氣滲透的能力,特別是用於檢測因濕氣侵入可能導致的材料分層(Delamination)或內部金屬層腐蝕等問題。

熱應力:機械疲勞的威脅

積體電路的封裝是由多種不同材料構成的複合體,例如:矽晶片、銅導線架、環氧樹脂封裝料等;這些材料各自擁有不同的熱膨脹係數(Coefficient of Thermal Expansion, CTE),當環境溫度發生變化時,不同材料會以不同的速率膨脹或收縮,從而在它們的介面處產生巨大的熱機械應力(Thermo-mechanical Stress),長期反覆作用下會導致機械疲勞失效。

- 溫度循環測試 (TC, Temperature Cycling):

依據JESD22-A104標準,TC測試讓待測元件在規定的高溫(如+150°C)和低溫(如-65°C)極端之間進行數百次至上千次的循環;溫度的轉換速率相對較慢,以確保整個元件內外都達到均勻的溫度,此測試目的在模擬產品在生命週期中可能經歷的溫度變化,以評估封裝的結構完整性,常見的失效模式包括焊點疲勞開裂、晶片破裂、封裝體開裂以及引線鍵合點失效等。

- 溫度衝擊測試 (TS, Thermal Shock):

依據JESD22-A106標準,TS測試是比TC更為嚴苛的熱應力測試;它要求元件在極短的時間內(通常在數秒內)從高溫環境轉換至低溫環境,反之亦然;這種劇烈的溫度衝擊會產生比TC更大的熱機械應力,其目的並非模擬真實使用情境,而是施加極端嚴苛的應力,以快速暴露產品結構中最脆弱的環節和潛在的設計缺陷。

在進行這些封裝級的可靠度測試之前,一個至關重要且常被忽略的步驟是「預處理(Preconditioning)」;根據JESD22-A113標準,預處理是後續如HAST、THB、TC等測試的強制性前置步驟,這個過程模擬了元件在被焊接到印刷電路板(PCB)上時所經歷的真實壓力:首先進行烘烤以去除內部濕氣,然後在特定的溫濕度環境下進行吸濕(模擬元件在工廠車間的暴露時間),最後通過數次模擬焊接的迴流焊高溫過程,此過程可能會在封裝內部引入一些潛在的、微小的損傷,例如:輕微的材料分層;隨後進行的HAST或TC等測試,其真正的目的之一就是評估這些在組裝過程中產生的潛在損傷,是否會在後續的環境壓力下擴散,並最終導致元件失效;若跳過預處理直接進行可靠度測試,即使元件通過了測試,其結果也可能不具備實際參考價值,因為它未能反映元件在經歷真實組裝過程後的真實可靠度表現;這個因果關係的理解,對於制定一個有效的、有意義的可靠度驗證計畫至關重要。

關鍵可靠度測試比較分析

為了提供一個清晰的概覽,下表總結了幾種核心可靠度測試的關鍵特性,便於工程師在規劃產品認證時進行快速參考與比較。

| 測試名稱 | JEDEC 標準 | 主要應力條件 | 一般測試時長 | 主要目標失效機制 |

|---|---|---|---|---|

| 高溫操作壽命 (HTOL) | JESD22-A108 | 高溫、動態電壓偏壓、全功能操作 | 1000 小時 | 晶片耗損機制 (電子遷移、氧化層崩潰、熱載子效應等) |

| 溫濕度偏壓測試 (THB) | JESD22-A101 | 85°C, 85% RH, 靜態電壓偏壓 | 1000 小時 | 封裝的抗濕性、慢速腐蝕、離子遷移 |

| 高加速應力測試 (HAST) | JESD22-A110 | >100°C, 85% RH, 壓力, 電壓偏壓 | 96 - 264 小時 | 快速評估封裝抗濕性、加速腐蝕 |

| 溫度循環測試 (TC) | JESD22-A104 | -65°C 至 +150°C 溫度循環 (慢速溫變) | 500 - 1000 週期 | 封裝材料CTE不匹配導致的機械疲勞 (焊點、晶片、封裝開裂) |

| 溫度衝擊測試 (TS) | JESD22-A106 | -65°C 至 +150°C 溫度衝擊 (快速溫變) | 100 - 500 週期 | 嚴苛應力下的封裝結構完整性、暴露潛在機械弱點 |

高溫操作壽命 (HTOL) 測試深度解析

在眾多可靠度測試方法中,高溫操作壽命(High Temperature Operating Life, HTOL)測試佔據著核心地位,它不僅是評估半導體元件長期可靠性的基石,更是連接實驗室加速測試與產品實際使用壽命的關鍵橋樑。

HTOL 的核心原理 (JESD22-A108)

根據JEDEC標準JESD22-A108的定義,HTOL是一種元件級別的可靠度測試,其核心方法是在遠高於正常工作範圍的溫度下,對元件施加動態的電壓偏置,並使其處於連續或間歇性的全功能操作狀態。

HTOL測試的主要目標並非篩選生產過程中的瑕疵品(那是Burn-in的任務),而是透過施加極端的熱應力與電應力,來加速那些與時間和溫度相關的、內在的物理耗損機制(Wear-out Mechanisms);藉由在一個可控的、相對較短的時間(通常為1000小時)內重現這些耗損過程,工程師可以科學地預測元件在正常使用條件下的長期可靠度表現,並估算其有效壽命的終點,即浴盆曲線中耗損期(Region III)的起始點;因此,HTOL測試的結果直接反映了一個產品在設計、佈局以及製造工藝上的內在穩健性(Robustness)。

失效物理學:HTOL 所加速的失效機制

HTOL測試的有效性,建立在對半導體固態物理失效機制的深刻理解之上,高溫與高電場的共同作用,能夠顯著加速以下幾種關鍵的耗損過程:

-

電子遷移 (Electromigration, EM):

在積體電路內部,金屬導線(通常為銅或鋁)承載著極高的電流密度;在導體中流動的電子會與金屬原子發生動量交換,如同持續不斷的「電子風」,將金屬原子從其晶格位置上推開;高溫會加劇金屬原子的熱振動,使其更容易被電子推動,而高電流密度則代表更強勁的「電子風」;長此以往,這種原子的定向遷移會在導線的某些區域造成金屬的虧空,形成「空洞」(Voids),最終導致開路;而在另一些區域則會造成金屬的堆積,形成「小丘」(Hillocks),可能引發與鄰近導線的短路。

-

時間相依性介電質崩潰 (Time-Dependent Dielectric Breakdown, TDDB):

在MOSFET電晶體中,閘極與通道之間的氧化層(Gate Oxide)是一層極薄的絕緣介電質;在持續的電場(由閘極電壓產生)和高溫作用下,這層介電質會逐漸退化,內部會緩慢形成微小的缺陷和漏電路徑;隨著時間的推移,這些缺陷會累積並最終形成一個貫穿整個氧化層的導電通道,導致閘極與通道之間的永久性短路,即「崩潰」(Breakdown);TDDB是決定現代CMOS技術可靠性的核心因素之一。

-

熱載子注入 (Hot Carrier Injection, HCI):

在電晶體工作的過程中,特別是在高電場區域(如靠近汲極的通道區域),電子或電洞(統稱為「載子」)可能被加速到獲得極高的動能,成為「熱載子」;這些高能的熱載子有足夠的能量克服位能障礙,注入到閘極氧化層中;一部分熱載子會被氧化層中的缺陷捕獲,成為固定電荷,這會改變電晶體的特性,例如:使其閾值電壓 (Vth) 發生漂移,或降低其跨導 (gm),從而導致電路性能下降甚至功能失效。

-

其他機制:

除了上述三種主要機制外,HTOL還能加速其他多種失效模式,例如:負偏壓溫度不穩定性(Negative Bias Temperature Instability, NBTI)、應力引發空洞(Stress-Induced Voiding)以及不同材料層之間的相互擴散(Inter-diffusion)等。

然而,深刻理解這些失效物理學也揭示了一個關鍵的細微之處:並非所有的失效機制都隨著溫度的升高而加劇;一個典型的反例就是熱載子注入(HCI),與直覺相反,HCI效應在低溫下通常更為嚴重,其物理原因在於,高溫下晶格的熱振動加劇(聲子散射增強),這會阻礙載子在電場中的加速過程,使其平均自由徑變短,從而難以獲得足夠高的能量成為「熱載子」;反之,在低溫下,晶格振動減弱,載子可以被更有效地加速,導致HCI效應增強;這表示僅僅依賴HTOL的可靠度驗證計畫,可能會錯過由HCI主導的潛在失效風險,因此,一個真正穩健的產品認證方案,必須將HTOL與低溫操作壽命(Low Temperature Operating Life, LTOL)測試相結合,以確保全面覆蓋在不同溫度區間內可能發生的主要耗損機制。

加速的科學:預測壽命

HTOL測試的精髓在於其「加速」能力,而將加速測試時間換算為實際使用壽命的科學依據,主要是基於阿倫尼烏斯方程式(Arrhenius Equation)。

- 阿倫尼烏斯方程式:

該方程式描述了化學反應速率與溫度之間的關係,並被廣泛應用於半導體可靠度領域,以量化由溫度驅動的失效機制的加速程度,其數學表達式為:

AFThermal = exp[ (Ea/k) * (1/Tuse - 1/Tstress) ]其中各項的定義如下:

- AFThermal:熱加速因數(Acceleration Factor),表示在應力溫度下測試1小時,相當於在正常使用溫度下運行了多少小時。

- Ea:活化能(Activation Energy),單位為電子伏特(eV)。這是整個模型中最關鍵也最具挑戰性的參數。它代表了觸發某一個特定失效機制所需的最低能量門檻。不同的失效機制擁有不同的活化能,例如電子遷移的 Ea 約為 0.5-0.7 eV,而TDDB的 Ea 約為 0.3-0.6 eV。

- k:波茲曼常數 (8.617×10-5 eV/K),一個物理常數。

- Tuse:產品在實際應用中的結溫(Junction Temperature),以絕對溫度(Kelvin)表示。

- Tstress:在HTOL測試中施加的應力溫度,同樣以絕對溫度表示。

- 實際應用舉例:

假設某個元件的主要失效機制是電子遷移,其活化能 Ea 為 0.7 eV,該元件的正常使用結溫 Tuse 為 55°C (328 K),而HTOL測試在 Tstress 為 125°C (398 K) 的條件下進行;根據阿倫尼烏斯方程式計算,其熱加速因數約為 78.6,這表示在125°C下進行1000小時的HTOL測試,其等效壽命相當於在55°C下運行 1000 × 78.6 = 78,600 小時,約合9年;透過這種方式,HTOL測試得以在合理的測試時間內,對產品的長期壽命做出科學的預測。

- 擴展模型:

對於同時受到溫度、濕度和電壓影響的測試(如HAST),阿倫尼烏斯模型可以被進一步擴展,以綜合考慮多種應力的加速效應。

活化能 Ea 的準確性,是整個HTOL壽命預測有效性的基石,使用一個不正確的 Ea 值,將會導致對產品壽命的預測出現巨大偏差,從而帶來嚴重的商業和信譽風險,例如,如果一個公司在開發新製程時,錯誤地沿用了舊製程的 Ea 值(假設為0.7 eV),但新製程中實際主導的失效機制其 Ea 僅為0.4 eV,那麼他們計算出的加速因數將會被人為地高估,這可能導致產品雖然通過了1000小時的HTOL測試,並被宣稱擁有10年的壽命,但實際上可能在3到4年後就會開始出現大規模的現場失效;這充分說明,可靠度工程不僅僅是執行標準測試,更需要在新技術導入階段進行深入的物理特性分析,以準確確定其主導失效模式及對應的活化能。

HTOL 的實踐:從標準到執行

將HTOL從理論應用於實踐,需要遵循嚴格的產業標準和執行細則。

- 產業要求:

- AEC-Q100:針對汽車電子,AEC-Q100根據元件的工作環境溫度,定義了不同的等級,例如,Grade 1要求元件能在-40°C至+125°C的環境溫度下工作,其對應的HTOL測試溫度即為125°C;Grade 0則要求更為嚴苛的+150°C測試溫度;無論哪個等級,通常都要求在測試1000小時後,失效率為零。

- 其他應用:商用、通訊或軍用產品的HTOL要求各不相同,通常會根據其預期的使用壽命和環境來定制測試條件。

- 執行細節:

- 抽樣計畫:為了確保測試結果具有統計學意義,樣品的選取必須遵循標準的抽樣計畫,如LTPD(Lot Tolerance Percent Defective,批容許不良率),一個常見的要求是,從至少3個不連續的生產批次中,抽取總共77顆樣品進行測試,並要求零失效;這確保了測試結果能夠反映生產製程的穩定性。

- HTOL測試板設計:HTOL測試板(也稱老化板或Burn-in板)是整個測試系統中最關鍵但最容易被低估的一環,它的作用是在長達數千小時的測試過程中,為每一顆待測元件(DUT)提供穩定且純淨的電源、精確的時脈和訊號、以及有效的散熱;一塊設計不良的測試板,可能會因為自身的不穩定而引發元件失效,或者無法為元件提供足夠的應力,這兩種情況都會導致測試結果的無效。

- 監控與讀點:在HTOL測試過程中,需要在指定的時間點(如168小時、500小時)將元件取出,進行功能性的電氣測試,這被稱為「中間讀點」(Interim Readouts);在1000小時測試結束後,還需要進行一次完整的最終測試,這些測試通常使用自動化測試設備(ATE)完成,目的在檢測是否存在災難性失效(功能完全喪失)或參數漂移(性能超出規格範圍)。

AEC-Q100 HTOL 要求

下表總結了AEC-Q100標準中不同溫度等級對HTOL測試的核心要求,為從事汽車電子設計與認證的專業人士提供清晰的參考。

| 等級 (Grade) | 環境操作溫度範圍 | HTOL 測試溫度 | 測試時長 | 典型應用場景 |

|---|---|---|---|---|

| Grade 0 | -40°C to +150°C | +150°C | 1000 小時 | 引擎蓋下等高溫區域 (如引擎或變速箱控制器) |

| Grade 1 | -40°C to +125°C | +125°C | 1000 小時 | 引擎蓋下大部分應用、安全系統 |

| Grade 2 | -40°C to +105°C | +105°C | 1000 小時 | 乘客艙內高溫區域 (如儀表板、音響系統) |

| Grade 3 | -40°C to +85°C | +85°C | 1000 小時 | 乘客艙內大部分應用 (如車身控制模組) |

解決方案分析:奧創系統的HTOL測試之道

奧創系統為專業的「測試工程系統整合商」(Test Engineering System Integrator),其核心價值乃為客戶提供貫穿整個產品週期的創新解決方案,服務範圍涵蓋從初期諮詢、可行性研究、平臺評估、新舊技術整合到流程優化的全方位支援。

這種商業模式的體現是,奧創系統透過與全球頂尖的專業技術領導者建立戰略合作夥伴關係,將其先進的、經過市場驗證的系統引進本地市場,並提供專業的在地化技術支援、應用開發與售後服務;其合作夥伴包括德國的射頻測試專家Becker Nachrichtentechnik、美國的視覺模擬技術領導者Quantum3D,以及奧地利的衛星訊號解決方案提供商OHB Digital Solutions 等。

這種策略使其能夠專注於解決特定領域內複雜且高價值的測試挑戰,目標市場鎖定在技術快速反覆運算、測試需求高度複雜的新興領域,如人工智慧、5G/6G通訊、光通訊模組、航空太空與國防等;透過為客戶提供量身定制的、一流的整合方案。

深度剖析:Becker TSQA系列射頻HTOL系統

針對先進半導體元件的HTOL測試需求,奧創系統提供的核心解決方案為Becker Nachrichtentechnik的TSQA系列射頻(RF)測試系統,該系統專為在可靠度測試期間,向待測物(DUT)提供高度精確、長期穩定且純淨的電氣應力訊號而設計,特別適用於AI晶片、光通訊模組等高頻高速元件的HTOL測試。

以下是對其核心子系統 TSQA-1X8PME 的技術規格分析,該系統是一個模組化的射頻測試子系統,專為HTOL應用而生。

- 關鍵規格:

- 頻率範圍:300 MHz 至 6 GHz,這個寬廣的頻率範圍不僅覆蓋了傳統的無線通訊頻段,也完全滿足5G FR1等新興標準的測試需求,具備良好的前瞻性。

- 輸出功率:每個輸出通道可提供高達 +40 dBm(即10瓦)的功率,這種高功率輸出能力,使其能夠對功率放大器(PA)等需要強大驅動訊號的有源元件進行極限條件下的壓力測試。

- 系統架構:採用標準的19吋、3U機架式設計,在緊湊的空間內整合了8個輸入通道和8個輸出通道,這種對稱的設計不僅能向DUT施加應力訊號,還能同時監測DUT的輸出響應(如輸出功率),實現閉迴路測試,從而更全面地評估元件在老化過程中的性能變化。

- 關鍵技術差異化:每通道獨立的自動電平控制(ALC)

該系統最核心、最具競爭力的技術優勢,在於其每個輸出通道都配備了獨立的、閉迴路的自動電平控制(Automatic Level Control, ALC)功能,ALC機制的工作原理是,系統會持續地、即時地監測實際傳輸到DUT埠的射頻功率,並透過一個快速反饋迴路,動態調整內部訊號源的輸出,以補償任何可能導致功率波動的因素,這確保了在長達數千小時的HTOL測試過程中,施加在DUT上的電氣應力能夠維持極高的穩定性。

這項技術直接解決了高功率、高頻率HTOL測試中最核心的挑戰,對於傳統的低功耗數位晶片,在1000小時內提供穩定的直流電壓相對簡單,但對於高功率的射頻元件,情況則完全不同;在長時間的高溫測試中,測試系統本身、連接電纜、接頭等都會因溫度漂移而產生顯著的損耗變化,這將導致最終到達DUT的實際功率發生波動,如果施加的電氣應力不恆定,那麼整個測試的加速因數就變成了一個未知數,測試結果也就失去了科學依據和可信度;ALC功能從根本上確保了應力條件的恆定性;此外,ALC還能有效抑制系統啟動瞬間可能產生的功率過衝(Overshoot),避免因瞬間的電氣過應力而意外損壞昂貴且敏感的待測元件;因此,由奧創系統整合的Becker HTOL 測試系統 所具備的ALC功能,並非一個普通的附加特性,而是實現有效、可重複的高階射頻元件HTOL測試的關鍵賦能技術。

目標應用與策略優勢

憑藉其高功率、高頻率、高穩定性的技術規格,奧創系統所提供的這套HTOL解決方案,完美契合了下一代半導體元件的可靠度驗證需求,在這些新興應用中,電氣應力的精確控制與熱應力的控制同等重要。

- 目標應用領域:

- AI與HPC加速器:現代AI晶片需要高速的記憶體介面和內部互聯,對訊號完整性和長期穩定性要求極高。

- 光通訊收發模組:用於資料中心和5G基站的光模組,其內部的高速驅動晶片和放大器需要在高溫下長期穩定工作。

- 5G/6G射頻前端模組(FEM)與功率放大器(PA):這些元件直接處理高功率的射頻訊號,其可靠度直接影響通訊品質和網路穩定性。

- 奧創系統的價值主張:

其策略優勢在於,將世界一流的德國精密工程技術(Becker)、應用整合和客戶支援相結合,向客戶交付的不僅僅是一台硬體設備,而是一套能夠解決其最棘手測試難題的完整方案;使客戶能夠在開發最先進、最高價值的產品時,有效降低其在可靠度認證環節的技術風險和時間成本。

奧創/Becker HTOL解決方案技術規格

下表詳細整理了奧創系統所提供的核心HTOL測試子系統TSQA-1X8PME的技術規格。

| 參數 | 規格 | 單位 | 備註(其重要性) |

|---|---|---|---|

| 頻率範圍 | 300 - 6000 | MHz | 覆蓋5G FR1及Wi-Fi 6/6E頻段,滿足現代無線通訊元件測試需求。 |

| 通道配置 | 8 輸入 / 8 輸出 | - | 高通道密度,支援並行測試多個DUT或DUT的多個埠。 |

| 最大輸出功率 | +40 | dBm | (10 W) 提供足夠的功率以對高功率放大器等元件進行極限壓力測試。 |

| 自動電平控制 (ALC) | 每個輸出通道獨立閉迴路 | - | 確保長期測試中施加於DUT的功率高度穩定,是測試有效性的關鍵。 |

| ALC 穩定性 | < ±0.2 | dB | 在整個測試期間,功率波動極小,保證了應力條件的一致性。 |

| 通道間隔離度 | > 80 | dB | 高隔離度可防止不同DUT之間的訊號串擾,確保測試結果的獨立性。 |

| 諧波抑制 | < -30 | dBc | 提供純淨的測試訊號,避免因測試系統引入的諧波干擾DUT。 |

| 介面 | LAN (Ethernet) | - | 便於遠程式控制制與自動化測試系統的整合。 |

| 機箱規格 | 19吋, 3U | - | 標準機架式設計,易於整合到現有的測試環境中。 |

結論

本文對半導體可靠度驗證的基礎理論、國際標準、關鍵測試方法,特別是高溫操作壽命(HTOL)測試,進行了系統性的闡述,並分析奧創系統在該領域提供的專業解決方案。

關鍵要點

- 可靠度驗證的戰略性:

可靠度驗證並非一系列孤立的測試,而是一項重點在於全面管理產品生命週期「浴盆曲線」的戰略性工程,從透過早期壽命測試篩選初期失效,到利用HTOL等加速壽命測試預測耗損期的到來,每項測試都有其明確的戰略目標。

- 失效物理學的核心地位:

選擇正確的測試方法,其前提是深刻理解潛在的失效物理機制,無論是因熱膨脹係數(CTE)不匹配導致的機械疲勞(由TC測試評估),還是濕氣引發的腐蝕(由THB/HAST評估),或是由溫度和電壓共同驅動的晶片內在耗損(由HTOL評估),理解其背後的物理原理是制定有效驗證計畫的基礎。

- HTOL的關鍵作用與挑戰:

HTOL是預測半導體元件長期耗損行為的基石,然而,其預測結果的有效性,完全取決於測試執行的嚴謹程度,這包括:採用基於正確活化能(Ea)的加速模型、設計能夠提供穩定電氣與熱學環境的測試硬體(如HTOL板)、以及精確施加並維持恆定的電氣應力,任何環節的疏忽都可能導致測試結果的偏差甚至完全失效。

對工程與品質的建議

- 對於新技術開發:

在導入新的半導體製程或封裝技術時,應將可靠度特性分析置於優先地位,在制定大規模的認證計畫之前,投入資源進行早期的物理特性分析,以識別該技術最可能的主導失效機制,並準確測定其對應的活化能等關鍵參數,這將為後續的壽命預測提供堅實的科學基礎,避免因錯誤的假設而導致的風險。

- 對於認證計畫規劃:

應採取一個整體的、平衡的視角來規劃產品認證,避免過度依賴單一的測試方法,例如,應將HTOL與LTOL測試相結合,以全面覆蓋不同溫度區間的耗損風險,同時,必須嚴格遵循JESD22-A113等標準,將預處理(Preconditioning)作為所有封裝級環境測試的必要前置步驟,以確保測試結果能夠反映真實世界的應用情境。

- 對於評估測試解決方案(服務或設備):

在選擇協力廠商測試實驗室或採購測試設備時,建議超越表面的規格參數(如最高測試溫度或通道數),應深入審查其提供應力條件的穩定性與精確性,例如奧創/Becker解決方案中至關重要的ALC功能;此外,還應評估供應商在測試治具(Test Fixture)設計上的專業能力,以及其在失效分析(Failure Analysis)方面的技術深度,如能夠在發生失效時快速定位並找出根本原因的能力,與產生失效的能力同等重要,一個優秀的合作夥伴不僅能執行測試,更能協助解決在測試中發現的根本問題。

參考資料

- 可靠性測試- 品質和可靠性- KEC Corporation | Trusted Power Semiconductor Company

- 可靠度測試可靠度驗證可靠度設計驗證RA Reliability Test - iST宜特

- AEC-Q100車規晶片驗證B1:HTOL - 高溫工作壽命實驗

- Chip Test socket工程師:可靠性測試中的HTOL測試解決方案 - 騰訊雲

- HTOL與LTOL的相關標準與失效模式詳解-CSDN博客

- 可靠性與資質認證| Cirrus Logic

- JEDEC 標準測試

- 晶片可靠性測試要求及標準解析_jesd22-a108-CSDN博客

- 半導體產品老化壽命試驗- 可靠度驗證 - 華證科技

- 科普小學堂第十期:THB/HAST 實驗介紹

- JEDEC半導體可靠度測試與規範 - 慶聲科技

- JEDEC半導體可靠度測試與規範

- HTOL和HALT實驗的基本原理和區別是什麼? - 可靠性試驗

- 高溫工作壽命 - 維琪百科,自由的百科全書

- 汽車電子產品的可靠性測試始終圍繞任務設定檔進行 - Monolithic Power Systems

- Quantum3D Delivers Next-Gen Visual Simulation System, Setting New Standards in Immersive Training Technology