預測性可靠度:超越傳統HTOL,為高功耗HPC與AI晶片建立整合性框架

可靠度悖論:在HPC/AI系統單晶片(SoC)的性能與壽命之間尋求平衡

HPC/AI晶片的全新常態

當代高效能運算(HPC)與人工智慧(AI)加速器的發展,正以前所未有的速度推動著半導體技術的極限,為了滿足巨量資料處理與複雜模型運算的需求,晶片設計已從傳統的單體式(Monolithic)架構,大規模轉向更為複雜的3D整合晶片(3D-IC)與小晶片(Chiplet)異質整合架構,此一轉變雖然帶來了驚人的運算能力,卻也引發了一個嚴峻的挑戰:功耗的急遽攀升;現今的先進HPC與AI晶片,其功耗輕易超過200W,並正朝向500W甚至1000W的驚人水平邁進,如此高的功率密度不僅在晶片的實際運行中產生巨大的散熱壓力,更在一個常被忽略卻至關重要的環節——可靠度測試與驗證階段,形成了前所未有的熱管理困境。

傳統可靠度範式的不足

長久以來,半導體產業依賴一套成熟的可靠度驗證方法學,其核心為高溫操作壽命(High Temperature Operating Life, HTOL)測試,此方法學的基礎建立在統計抽樣計畫,如允收水準(Lot Tolerance Percent Defective, LTPD),以及基於簡單「通過/失敗」(Pass/Fail)二元標準的判斷之上,然而,這套為相對簡單、低功耗的單體式晶片所設計的傳統範式,在面對當今高度整合、高功耗的HPC/AI晶片時,已顯得捉襟見肘。傳統HTOL測試僅能回答「有多少樣本在規定時間內失效」,卻無法揭示元件退化的軌跡、潛在的失效機制,更無法為那些要求零停機時間(Zero-Downtime)的關鍵應用(如資料中心、自動駕駛系統)提供足夠的壽命保證,傳統方法的顆粒度過於粗糙,無法有效篩選出那些雖然通過測試,卻存在潛在缺陷的「邊緣晶片」(Marginal Chips),這些晶片正是導致現場失效率(Field Failure Rate)攀升的隱形殺手。

新興的衝突:設計壽命與任務需求的鴻溝

一個日益尖銳的衝突正在半導體價值鏈中浮現,晶圓代工廠(Foundry)出於商業考量,其設計的元件壽命目標通常設定在三至七年,這對於消費性電子產品而言或許足夠,然而,對於資料中心、電信基礎設施、航太國防等需要長達十年甚至更長運行壽命的關鍵任務應用(Mission-Critical Applications)而言,這樣的設計壽命顯然存在巨大落差;對於像世芯(Alchip)和創意電子(GUC)這樣的頂尖ASIC設計服務公司而言,其產品正是驅動這些關鍵系統的核心,如何彌合晶片固有設計壽命與終端客戶嚴苛任務需求之間的鴻溝,已成為當前最核心的可靠度工程挑戰。

核心論點:整合性、數據驅動框架的必要性

為確保下一代高功耗HPC與AI晶片的可靠度,必須進行一次徹底的範式轉移,不能再滿足於被動地計算失效數量,而必須轉向主動地預測失效行為,這需要建立一個整體的、數據驅動的閉環系統;此框架必須緊密整合四大關鍵支柱:

- 在測試過程中實現精準、動態的主動式熱管理;

- 透過晶片內建的遙測技術(On-Chip Telemetry)進行精密的即時感測;

- 利用機器學習驅動的預測性分析,從海量數據中發掘潛在風險;

- 應用失效物理(Physics-of-Failure, PoF)模型,將加速測試數據精確地轉譯為對真實世界使用場景的壽命預測。

這種轉變的背後,不僅是技術的演進,更是經濟效益的驅動,在複雜的3D-IC或小晶片封裝中,其報廢成本是呈幾何級數累積的;一個包含四顆小晶片的先進封裝,若其中一顆在最終測試中失效,其損失不僅是該顆小晶片的成本,而是整個昂貴封裝的總和;這使得「已知良好晶粒」(Known Good Die, KGD)的概念變得至關重要,也對可靠度測試方法提出了更高的要求:它必須在封裝前就精準識別出那些可能在未來失效的「邊緣晶片」,因此,從「通過/失敗」邁向「預測性可靠度」,其根本動機不僅是為了降低現場返修率(RMA),更是在生產流程的早期階段,透過精準篩選,避免將高成本、高風險的元件投入到最終的昂貴封裝中,從而實現良率與成本的雙重優化。這正是產品工程師在管理專案預算與風險時,必須面對的嚴峻現實。

熱管理的迫切性:高功耗HTOL測試中的主動式熱控制

測試環境中的自發熱物理學

在HTOL測試的核心,是透過阿倫尼烏斯方程式(Arrhenius Equation)利用高溫來加速元件的老化過程,從而預測其在正常操作溫度下的壽命,此模型的有效性建立在一個關鍵假設之上:待測元件(Device Under Test, DUT)的接面溫度(Junction Temperature, Tj)是已知且受控的;然而,對於功耗超過200W的HPC晶片而言,這個假設在傳統的HTOL測試環境中已然失效;當這些高功耗元件在HTOL測試爐中被施以動態的壓力向量(Stress Patterns)時,其內部會產生巨大的熱量,導致顯著的「自發熱」(Self-Heating)效應,這使得DUT的實際Tj可能遠高於測試爐設定的環境溫度,甚至可能出現高達數十度的溫差;更嚴重的是,在複雜的多晶片封裝中,由於各個小晶片的功耗分佈不均,會產生極不均勻的熱梯度(Thermal Gradients),某些區域可能成為「熱點」(Hotspots),而其他區域溫度相對較低;這種不受控且不均勻的Tj分佈,不僅使得基於單一環境溫度的阿倫尼烏斯模型完全失效,導致壽命預測結果毫無意義,更可能對元件本身造成非預期的過度應力,引入新的失效模式。

自動化測試設備(ATE)中的主動式熱控制(ATC)

為了解決高功耗元件在測試過程中的自發熱問題,半導體測試產業發展出了主動式熱控制(Active Thermal Control, ATC)技術,與傳統依賴整個測試爐進行被動加熱的方式不同,ATC系統能夠在單一DUT層級上進行精準、動態的溫度調節;現今領先的自動化測試設備(ATE)與分類機(Handler)供應商,已能夠應對高達800W功耗的先進ATC解決方案,這些系統的關鍵特性包括:

-

高功率散熱能力:

能夠即時移除DUT產生的數百瓦熱量,將Tj穩定在設定的目標溫度。

-

多站點獨立控制:

在並行測試多個DUT時,能為每一個DUT提供獨立的溫度控制,應對不同元件之間因製程變異導致的漏電流(Leakage Current)差異。

-

三溫測試能力:

在單次插入(Single Insertion)中完成高、中、低三種溫度的測試,大幅提升測試效率。

-

快速熱響應:

具備極快的溫度響應速度(例如 >125°C/秒),能夠追蹤並補償因測試向量變化而引起的瞬時功耗波動。

這些基於空氣或液體冷卻的ATC技術,代表了當前量產測試中應對高功耗挑戰的產業標準。

下一個前沿:將資料中心級冷卻技術引入測試插座

然而,隨著HPC與AI晶片的功耗持續向千瓦等級邁進,即使是目前最先進的ATC技術也將面臨極限,HTOL測試的未來,勢必需要將原本應用於高密度資料中心的頂級冷卻技術,直接整合到測試插座(Test Socket)和老化板(Burn-in Board)的設計之中,這場從「測試環境」到「微型資料中心」的技術轉移,正催生出兩種革命性的解決方案。

泵送式雙相流冷卻(Pumped Two-Phase Cooling)

泵送式雙相流冷卻系統借鑒了高效熱管的原理,但透過主動泵送提供了更強大的散熱能力和控制彈性,其工作原理是將一種介電(非導電)冷卻液(如R134a等冷媒)泵送到與晶片緊密接觸的冷板(Cold Plate)上,當冷卻液接觸到高溫的晶片表面時,會迅速沸騰汽化,在相變過程中吸收大量的潛熱(Latent Heat of Vaporization),這種利用潛熱的散熱方式效率極高,相比傳統的單相水冷,它可以在更低的流速下帶走更多的熱量。

對於HTOL應用而言,此技術的關鍵優勢在於其卓越的溫度均一性,由於相變發生在近乎恆定的溫度下,即使將多個高功耗DUT串聯在同一個冷卻迴路中,也能確保每個DUT的溫度保持高度一致,這對於需要進行大規模並行老化測試的場景至關重要。

直達晶片(Direct-to-Chip)與浸沒式冷卻(Immersion Cooling)

當功耗密度達到極致時,直達晶片與浸沒式冷卻成為了終極解決方案,以ZutaCore的HyperCool技術為例,它採用雙相、直達晶片的冷卻方法,能夠處理超過2800W的處理器功耗,在這種架構中,冷卻系統直接作用於晶片本身或其散熱頂蓋(IHS),移除了傳統散熱器和風扇等中間環節,最大限度地降低了熱阻;而浸沒式冷卻則是將整個老化板或DUT完全浸泡在介電冷卻液中,透過液體的沸騰來帶走熱量,提供了無與倫比的散熱效率和溫度穩定性。

這些尖端技術的出現,標誌著一個重要的趨勢:HTOL測試插座的設計,已從一個傳統的機電工程問題,演變為一個涉及流體動力學、熱力學和相變物理的複雜熱工程挑戰;對於ASIC設計公司而言,這代表其可靠度測試的硬體策略,必須與其客戶的資料中心基礎設施策略一樣,具備同樣的複雜度和前瞻性。

| 技術 | 最大散熱功率 (W) | Tj 控制精度 (°C) | 響應時間 | 熱均勻性 | 多站點擴展性 | 系統複雜度與成本 |

|---|---|---|---|---|---|---|

| 被動式散熱片/傳統烤箱 | < 50 | > ±10 | 慢 | 差 | 差 | 低 |

| 氣冷式ATC | 100 - 300 | ± 2-5 | 中等 | 中等 | 好 | 中等 |

| 液冷/冷媒式ATC | 300 - 800+ | ± 1-2 | 快 | 好 | 好 | 高 |

| 泵送式雙相流冷卻 | 1000+ | < ±1 | 非常快 | 極佳 | 極佳 | 非常高 |

| 直達晶片/浸沒式冷卻 | 2000+ | < ±0.5 | 即時 | 頂級 | 好 | 非常高 |

此表格為產品與可靠度工程師提供了一個清晰的決策框架,它將現有的熱管理解決方案與未來產品不斷攀升的功耗路線圖直接對應,明確回答了關鍵問題:「對於未來200W、500W乃至1000W的晶片驗證,需要採用哪種等級的熱管理方案?」

精密原位感測:準確可靠度模型的基石

接面溫度(Tj)的核心地位

在可靠度物理學的宏偉殿堂中,接面溫度(Tj)無疑是那塊最重要的基石,無論是描述熱激活失效機制的阿倫尼烏斯方程式,還是預測電子遷移(Electromigration)現象的布萊克方程式(Black's Equation),Tj都是其中最為關鍵、最具影響力的變數;任何Tj輸入值的微小偏差,都會被指數級放大,最終導致壽命預測結果的巨大誤差;因此,可以毫不誇張地說,一個不準確的Tj測量,將使得所有後續的可靠度建模與壽命預測工作都失去意義,獲取精準、即時的Tj數據,是從傳統HTOL邁向預測性可靠度的前提與基礎。

晶片內建熱敏二極體與TSEP的挑戰

現代SoC普遍內建了用於溫度監控的感測器,通常是利用半導體元件(如二極體或BJT)的電氣特性隨溫度變化的原理,這些被稱為溫度敏感電氣參數(Temperature Sensitive Electrical Parameters, TSEPs),儘管它們提供了監控晶片內部溫度的途徑,但在追求高精度可靠度建模的應用中,這些標準感測器卻面臨著嚴峻的挑戰。

-

內在的不準確性:

TSEP的測量精度受到多種物理因素的制約,首先是二極體的「非理想因子」(Non-ideality Factor, n),這個參數的微小偏差會直接影響溫度換算的準確性;其次是感測器路徑上的「串聯電阻」(Series Resistance),經驗顯示,每1歐姆的串聯電阻就會導致約0.5°C的溫度讀數誤差,再加上晶片製造過程中固有的製程變異,會導致不同晶片甚至同一晶片上不同感測器之間的特性存在差異,造成內部監控讀數與外部測量值之間出現不匹配。

-

校準的夢魘:

為了克服內在的不準確性,每個TSEP在使用前都必須經過嚴格的校準,傳統的校準過程通常是離線(Offline)的,需要在實驗室環境下,將晶片置於精確控制的溫控平台上,測量不同溫度下的TSEP值,從而建立一個查找表(Look-up Table)或線性擬合模型。這個過程不僅耗時、成本高昂,而且其結果可能因為元件在長期使用中的老化(Aging)而逐漸失效,失去準確性。

-

精度與現實的差距:

可靠度物理模型要求Tj輸入的精度達到1°C以內,以確保預測結果的有效性;然而,標準的晶片內建感測器在未經精細校準的情況下,其典型精度往往在±4°C甚至更差的範圍內,這種精度與需求之間的巨大鴻溝,是當前可靠度工程領域面臨的一個根本性難題。

實現真實Tj的策略

要跨越上述鴻溝,需要採用更為先進與系統化的方法來獲取真實的Tj。

-

線上、非侵入式校準:

近年來的研究提出了一種創新的線上校準方法,目的在解決傳統校準的弊端,該方法利用功率元件在正常啟動和運行過程中自然出現的幾個特定熱穩態,透過測量這些狀態下的TSEP和可輕易獲取的散熱器溫度(Th),便能以非侵入的方式,即時計算出TSEP與Tj之間的精確轉換關係;儘管此方法在實現上仍有其複雜性(例如:需要特定的操作狀態和較長的穩定時間),但它指明了一條通往更實用、更準確的即時校準之路。

-

多感測器數據融合:

與其依賴單一類型的感測器,一個更穩健的策略是採用多感測器數據融合,這表示在晶片上佈局多種類型的溫度感測器,例如:傳統的熱敏二極體、對溫度敏感的環形振盪器(Ring Oscillators),甚至利用材料光學特性隨溫度變化的原理(如光譜的半峰全寬(FWHM)位移);透過融合來自不同物理原理感測器的數據,不僅可以交叉驗證,提高整體測量精度,還能夠有效偵測並補償單一感測器因老化而產生的漂移。

-

基於遙測的熱成像圖:

最先進的方法是從測量「單點平均溫度」轉向繪製「即時熱成像圖」,透過在晶片上戰略性地分佈一個由大量微型溫度感測器組成的網路(例如ProteanTecs等提供的感測器IP),可以即時捕捉整個晶粒的溫度分佈,這不僅能提供一個更具代表性的平均Tj值,更重要的是能夠精確識別出局部熱點的位置和強度,對於分析由熱梯度引發的熱機械應力(Thermo-mechanical Stress)等失效模式而言,這種空間解析度的資訊至關重要。

這一切努力的背後,揭示了一個深刻的現實:在追求現代化可靠度所需的非侵入式、即時數據與獲取這些數據所需的侵入式、離線校準方法之間,存在著根本性的矛盾;線上校準方法的複雜性本身,就凸顯了這個核心問題的嚴重性,這也預示著,未來五年在可靠度物理領域的最大突破,可能不是一個新的失效模型,而是一款低成本、高精度、可自我校準的晶片內建溫度感測器;對於工程師而言,這可能代表著在選擇和授權第三方IP時,必須積極且嚴格地審視其內建溫度感測器的精度規格和校準要求。

超越通過/失敗:可靠度數據採集與分析的新範式

屬性統計的局限性

傳統的HTOL測試在數據分析層面,遵循的是一種基於屬性(Attribute-based)的統計方法,其核心是預先設定一個抽樣計畫,例如基於LTPD(批容許不良率)標準,從生產批次中抽取一定數量的樣本(例如,230個樣本中允許0個失效,或668個樣本中允許3個失效)進行測試 4。測試結束後,僅僅統計失效樣本的數量。如果失效數在可接受範圍內,則該批次被判定為「通過」。這種方法雖然在宏觀的製程品質控制上具有統計學意義,但其資訊價值極低。它將每個DUT視為一個黑盒子,最終只產出一個二元結果(通過或失敗),完全忽略了那些「存活」下來的元件在測試過程中所發生的細微變化。它無法回答更深層次的問題:存活元件的健康狀況如何?它們的性能退化了多少?它們的剩餘壽命還有多長?

向變數數據的轉變:通用晶片遙測技術(UCT)

要真正實現預測性可靠度,就必須從收集「屬性數據」轉向收集「變數數據」(Variable Data),這場革命的核心,是由ProteanTecs等公司率先提出的通用晶片遙測技術(Universal Chip Telemetry, UCT)概念。

-

晶片內建代理(On-Chip Agents):

UCT的基礎是在晶片設計階段,無縫嵌入一系列微小、非侵入式的智慧財產權(IP)模組,這些模組被稱為「代理」(Agents),這些代理就像是植入晶片內部的微型感測器和監測器,能夠在晶片運行時,即時監控關鍵的物理和電氣參數;代理的種類繁多,涵蓋了性能與退化監控(例如測量關鍵路徑延遲)、時序裕度(Timing Margin)監控、電源完整性(例如偵測電壓降Vdroop)以及I/O通道健康狀況等。

-

深度數據分析(Deep Data Analytics):

這些代理在晶片的整個生命週期中(從晶圓測試到現場運行),持續不斷地產生海量的參數化數據流,這種數據遠比傳統的「通過/失敗」資訊豐富,被稱為「深度數據」(Deep Data),這些深度數據構成了後續先進分析的基礎,為我們打開了一扇前所未有的窗戶,得以窺探每一顆晶片內部的真實狀況。

應用機器學習進行預測性分級

僅有深度數據是不夠的,如何從海量、高維度的遙測數據中提取有價值的資訊,是更大的挑戰,這正是機器學習(ML)發揮關鍵作用的地方,ML演算法能夠將原始的遙測數據轉化為可操作的可靠度洞察。

-

異常值檢測(Outlier Detection):

傳統的異常值篩選方法,如部分平均測試(Part Average Testing, PAT),依賴於簡單的統計分佈,而基於ML的方法則強大得多,例如,透過靜態電流(IDDQ)預測,ML模型可以基於晶片的設計和製程資訊,為每一顆晶片預測其應有的正常IDDQ值;在測試中,將實際測量值與預測值進行比較,任何顯著的偏差都可能表示存在傳統測試無法發現的潛在漏電缺陷;同樣,透過時序裕度檢測,內建的代理能夠監控數百萬條邏輯路徑的時序裕度,ML模型可以學習正常的裕度分佈,並識別出那些雖然時序通過測試,但裕度異常低的「邊緣晶片」,這些晶片在未來極有可能因為老化或電壓波動而失效。

-

晶片「家族」分類(Family Classification):

這是一項關鍵的創新,傳統方法將同一批次的所有晶片視為一個整體,用統一的標準進行評判;而UCT和ML技術可以根據每顆晶片在初始測試(如晶圓測試)中表現出的獨特參數行為(Parametric Behavior),將它們自動分類為不同的「家族」(Families);同一家族的晶片具有相似的內在特性,這種分類為每一顆晶片建立了一個高度個人化的基準線,在此基礎上,後續的任何性能退化或異常行為都可以被更精確地量測和識別,極大地提升了監控的靈敏度和準確性。

-

案例研究:GUC與ProteanTecs的合作:

ASIC設計領導者GUC與ProteanTecs的合作,為這一新範例的實際應用提供了絕佳的例證,在其GLink™高速裸晶對裸晶(Die-to-Die)介面的測試晶片中,GUC整合了ProteanTecs的互連監控解決方案,這項合作的公開白皮書揭示,透過內建的遙測代理,GUC能夠獲得對高速介面內部狀況前所未有的可視性,包括對每一條通道進行參數化分級,從而加速了特性分析過程,並為其客戶提供了在實際應用中進行壽命監控的能力,這證明了對於HPC小晶片設計中的關鍵環節——高速互連的可靠度保證,UCT技術正扮演著不可或缺的角色。

| 參數 | 傳統HTOL | 預測性HTOL |

|---|---|---|

| 主要目標 | 符合規範 (Compliance) | 預測壽命 (Prediction) |

| 關鍵指標 | 失效數量 (Failure Count) | 退化速率 (Degradation Rate) |

| 數據類型 | 二元 (通過/失敗) | 參數化遙測 (Parametric Telemetry) |

| 分析方法 | LTPD 統計 | 機器學習/人工智慧 (ML/AI) |

| 熱控制 | 被動/烤箱 (Passive/Oven) | 主動/每DUT (Active/Per-DUT) |

| 失效洞察 | 何時失效 (When it failed) | 為何及如何失效 (Why & How it's failing) |

| 產出 | 通過/失敗報告 (Pass/Fail Report) | 剩餘使用壽命預測 (RUL Prediction) |

此表格清晰地總結了本報告的核心論點,它不僅展示了技術的演進,更揭示了一場深刻的思維模式轉變,對於可靠度工程師而言,這代表著從一個被動的「記分員」,轉變為一個主動的「診斷師」和「預言家」。

這種轉變的深遠影響在於,它為ASIC設計公司創造了一項全新的、極具價值的戰略資產:一個覆蓋全生命週期的「晶片群體行為數據庫」,當來自數百萬顆晶片的遙測數據,從晶圓測試、封裝測試、系統級測試,一直到最終的現場運行,被持續不斷地匯總到一個統一的雲端平台時,一個強大的分析能力便應運而生;可靠度工程師現在可以提出並回答以往無法想像的問題,例如:「來自某片晶圓特定角落的晶片,在經過1000小時HTOL後,是否表現出高於平均水平的退化率?」或者「晶圓測試時的某個特定時序裕度指標,與客戶現場發生的電源相關故障之間是否存在關聯?」這種從現場到晶圓廠的精準數據反饋迴路,在過去是完全不可能的;它將可靠度工程從一門基於粗略統計和事後分析的學科,轉變為一門由數據科學驅動的、具備主動預測和持續改進能力的工程學;而ProteanTecs與Advantest、Teradyne等ATE巨頭的合作,更代表這種深度數據分析正在被直接整合到測試機台的工作流程中,實現了即時的、數據驅動的生產決策。

從加速數據到現場現實:失效物理(PoF)模型的角色

關鍵磨損機制工程評述

如果說晶片遙測技術提供了「數據」,那麼失效物理(Physics-of-Failure, PoF)模型則提供了將這些數據轉化為「知識」的科學框架,PoF的核心思想是,透過理解導致元件失效的根本物理、化學、機械和電學機制,來建立數學模型,從而預測元件在特定應力條件下的壽命;要準確預測現代HPC晶片的壽命,必須對其主要的磨損(Wear-out)機制有深刻的理解,在先進的CMOS製程中,四種主要的失效機制主導了元件的長期可靠度:

-

負偏壓溫度不穩定性(Negative Bias Temperature Instability, NBTI):

此效應主要影響PMOS電晶體,在負閘極電壓和高溫的共同作用下,氧化層與矽的介面會產生陷阱(Interface Traps),導致電晶體的臨界電壓(Threshold Voltage, Vth)發生漂移,性能下降,NBTI是先進製程中最主要的可靠度挑戰之一,其退化程度對溫度和電壓極為敏感。

-

熱載子注入(Hot Carrier Injection, HCI):

當電晶體通道中存在高電場時,電子或電洞會被加速到足夠高的能量(成為「熱載子」),並被注入到閘極氧化層中,造成永久性損傷;HCI會影響NMOS和PMOS,導致驅動電流下降、臨界電壓漂移等問題,尤其在高速、高頻率切換的電路中更為顯著。

-

電子遷移(Electromigration, EM):

在高電流密度下,流動的電子會與金屬導線中的金屬原子發生動量交換,如同「電子風」一般,將金屬原子從其晶格位置上推開,導致導線中出現空洞(Voids)或在別處堆積成小丘(Hillocks),最終造成開路或短路。其失效速率由著名的布萊克方程式描述,與電流密度和溫度呈指數關係。

-

時間相依介電質崩潰(Time-Dependent Dielectric Breakdown, TDDB):

閘極氧化層作為電晶體的核心絕緣層,在持續的電場和高溫作用下,其內部會逐漸形成缺陷,最終形成一條導電路徑,導致閘極的永久性擊穿,隨著製程節點的微縮,閘極氧化層變得越來越薄,使得TDDB成為一個日益嚴峻的挑戰。

建立多重應力壽命模型

傳統的加速測試通常只考慮單一的、靜態的應力條件(例如,恆定的125°C和1.1倍額定電壓),然而,真實世界中的晶片承受的是動態的、多變的應力,要建立一個能夠反映真實情況的壽命模型,就必須超越簡單的加速因子(Acceleration Factor, AF)計算,這需要利用前述章節中獲取的精準、即時的遙測數據(如Tj(t), V(t), I(t)),將其作為PoF數學模型的動態輸入;其目標是計算在動態應力下的「累積損傷」(Cumulative Damage),而不是基於單一靜態應力點的外推,例如,可以將晶片的運行時間切分成微小的時間片,計算每個時間片內由NBTI、HCI、EM和TDDB造成的微小損傷,然後將這些損傷隨時間累積起來,直至達到失效閾值。

關聯真實世界的任務剖面

壽命預測的最終目的是評估晶片在客戶實際應用場景中的表現,這就需要將加速測試的結果與客戶的「任務剖面」(Mission Profile)相關聯,典型的資料中心伺服器,其負載並非恆定不變,而是在白天處理高峰流量,夜間則處於較低負載狀態;這種工作負載的波動,直接轉化為晶片內部溫度和電壓的動態變化;透過使用如「雨流計數法」(Rain-flow Counting)等技術,可以對客戶提供的任務剖面進行分析,將其分解為一系列不同幅度和持續時間的應力循環;然後,將這些應力循環輸入到前面建立的累積損傷模型中,就可以計算出晶片在整個預期服役年限內(例如10年)的總損傷量,從而判斷其是否能夠滿足客戶的壽命要求,這個過程,才真正實現了從實驗室加速數據到現場使用現實的精確映射。

量化壽命:剩餘使用壽命(RUL)

這種先進分析方法的最終產出,不再是一個簡單的「通過/失敗」結論,而是一個量化的、可預測的指標——剩餘使用壽命(Remaining Useful Life, RUL),RUL可以針對單一晶片進行預測,也可以對整個群體進行統計分佈預測,這一指標具有巨大的商業價值:它使得預測性維護(Predictive Maintenance)成為可能,例如:在系統偵測到某個AI加速卡RUL即將耗盡時,可以提前發出警報並安排更換,它也為制定更精確的保固條款和服務等級協定(SLA)提供了數據支援,更進一步,它甚至可以在現場實現動態的性能調控,例如:系統可以主動降低一顆正在加速退化的晶片的時脈頻率或電壓,以犧牲部分性能為代價,來延長其服務壽命,確保整個系統的持續穩定運行。

| 機制 | 物理描述 | 主要應力源 | 受影響結構 | 代表性PoF模型 |

|---|---|---|---|---|

| NBTI | 負偏壓與高溫下,Si-SiO2介面產生陷阱,導致Vth漂移。 | 溫度、電壓、時間 | PMOS閘極介電層 | ΔVth ∝ A ⋅ exp(−Ea/kT) ⋅ tn |

| HCI | 高電場下,載子獲取高能量並注入閘極氧化層,造成損傷。 | 電壓、頻率、溫度 | NMOS/PMOS通道區域 | τ ∝ B ⋅ Isub-m ⋅ Idm-1 ⋅ exp(φit / qλEm) |

| EM | 高電流密度下,「電子風」推動金屬原子遷移,導致開路/短路。 | 電流密度、溫度 | 金屬互連線、通孔 | MTTF = A ⋅ J-n ⋅ exp(Ea/kT) (Black's Eq.) |

| TDDB | 持續電場與高溫下,閘極介電質內部形成缺陷,最終導致擊穿。 | 電壓、溫度、面積 | 閘極介電層 | tBD ∝ C ⋅ exp(γEox - Ea/kT) |

此表格為可靠度工程師提供了一個關鍵的技術參考,它將抽象的「退化」概念與具體的物理過程和用於預測它們的數學模型聯繫起來,使得PoF方法論變得具體而易於理解。

在應用這些PoF模型時,一個至關重要的考慮是「木桶效應」或「最弱環節」問題,一個晶片的整體壽命,是由最先發生的那個失效機制所決定的;研究數據顯示,隨著製程節點的演進,主導的失效機制會發生變化,例如,在較舊的製程節點,由於導線尺寸較大,電子遷移可能是主要考量;然而,在先進的5奈米節點,由於使用了更薄的閘極氧化層和更高的電場,TDDB和NBTI/HCI的影響可能變得更為顯著,這時可靠度工程師不能再依賴一個單一的、通用的活化能(Activation Energy, Ea)值(例如,業界經驗法則中常用的0.7 eV 4)來進行所有計算。一個現代化的可靠度計畫,必須利用晶片內建的遙測技術,去監控與所有四種主要機制相關的特定參數,並行運行多個PoF模型;最終預測的設備壽命,應該是所有單一模型預測壽命中的最小值,這要求一個遠比傳統方法更為複雜和精密的建模與數據採集基礎設施。

整合性HTOL生態系統:為預測性可靠度進行架構設計

現代預測性HTOL系統的架構

將前述章節的理念與技術融合,一個現代化的預測性HTOL系統 架構便浮現出來,它不再是一個孤立的設備,而是一個由多個子系統緊密協同工作的整合性生態系統,其核心組件包括:

-

測試平台(The Test Platform):

這是整個系統的基礎;它必須是一個靈活、高功率的HTOL系統,能夠為每一個DUT提供獨立的電源和訊號控制,系統需要具備高度的可程式化能力,以適應不同晶片的複雜測試需求。

-

熱管理解決方案(The Thermal Solution):

如前所述,一個整合了高性能ATC或先進雙相流冷卻技術的系統是必不可少的,它必須能夠精確控制每個DUT的Tj,並即時響應功耗的動態變化,為PoF模型提供穩定、準確的溫度輸入。

-

數據採集系統(The Data Acquisition System):

系統必須具備高速、高容量的數據記錄能力;它不僅要記錄傳統的系統級數據(如電源電壓、電流),更重要的是,要能夠捕獲並記錄來自晶片內部的海量遙測數據流。

-

分析引擎(The Analytics Engine):

這是系統的大腦;它通常是基於雲端的軟體平台,負責執行即時監控、基於ML的異常檢測與分級、以及最終的PoF建模與RUL預測。

對HPC/AI產品與可靠度工程的考慮事項

為了成功應對高功耗HPC/AI晶片帶來的可靠度挑戰,並從傳統的「通過/失敗」模式轉向先進的「預測性可靠度」框架,可考慮以下幾點:

擁抱「為可視性而設計」(Design for Visibility)的哲學

最根本的戰略轉變,是將可靠度的考量前移至設計週期的最前端,將晶片內建監控IP(如UCT代理)視為晶片架構的標準組成部分,而非一個可有可無的附加選項,這正是現代「可測試性設計」(DFT)和「可信賴性設計」(DFR)理念的精髓,在設計初期就植入這些「眼睛」和「神經」,才能在晶片的整個生命週期中獲得對其內部狀態的持續可視性,這是所有後續分析和預測的基礎。

建立統一的可靠度數據平台

打破設計、製造、測試和現場應用之間的數據孤島,建立一個統一的、基於雲端的數據平台,用以匯總來自產品全生命週期的遙測數據和測試結果,這個平台將成為可靠度的「單一事實來源」(Single Source of Truth),不僅能夠實現第四章中討論的強大反饋迴路,驅動設計和製程的持續改進,還能為不同團隊(設計、測試、品保、現場支援)提供協同工作的共同語言和數據基礎。

建立戰略性的生態系統合作夥伴關係

在當今高度專業化和複雜化的半導體產業鏈中,可靠度保證已不再是任何一家公司可以獨立完成的任務,ASIC設計公司須與其價值鏈上的關鍵夥伴建立深入、協同的戰略關係,這包括與晶圓代工廠、封裝測試代工廠(OSATs),以及關鍵技術供應商的緊密合作,GUC與ProteanTecs的合作模式便是一個典範,透過這種合作,確保數據標準、測試方法學和可靠度目標在整個供應鏈中得到統一和貫徹,從而實現端到端的品質保證。

未來展望:可靠度即服務(Reliability-as-a-Service)

本文所闡述的框架,不僅是解決當前挑戰的方法,更指向了一個全新的未來,在這個未來中,可靠度不再是一次性的驗證事件,而是一種持續的、動態的評估過程,透過現場運行的晶片內建遙測技術,可以實現對整個伺服器集群的健康狀況進行即時監控和預測性維護,系統可以根據每顆晶片的退化狀態和工作負載,進行自我調整的性能優化(例如,工作負載感知下的自動電壓調節);更具想像力的是,這可能催生出全新的商業模式,即「可靠度即服務」,晶片或系統供應商可以根據客戶的需求,提供不同等級的可靠度保證,並將其作為產品的一部分進行收費,從而創造新的收入來源,並極大地提升產品的附加價值。這將是半導體產業從銷售「硬體」到銷售「性能與保障」的終極體現。

關於奧創系統科技

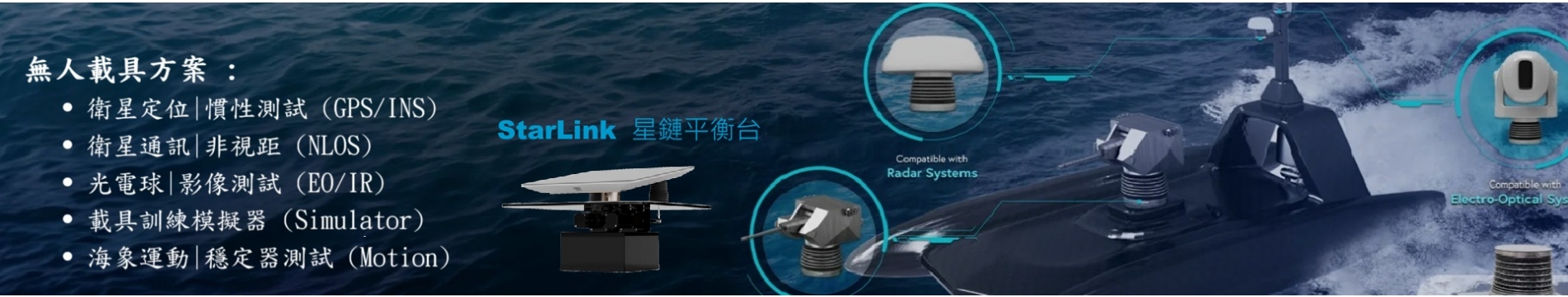

奧創系統科技的專業技術服務橫跨多個尖端領域,展現其深厚的技術底蘊與市場洞察力:

- 航太國防應用: 提供無人載具、訓練模擬器、衛星干擾防禦等關鍵系統。

- 半導體量測設備: 涵蓋探針平台、高溫壽命測試 (HTOL) 等方案。

- 運動模擬平台: 包含高精度六軸平台與產業訓練模擬器。

- 射頻 (RF) 測試儀器: 從訊號產生、分析到完整測試系統建置。

- 光電影像模擬: 提供紅外線目標投影器、黑體校正源等專業設備。

- 車用製造與衛星測試: 針對新興的車用雷達與低軌衛星產業提供測試方案。

- 客製化系統: 包含電波/電磁暗房建置與自動化軟體開發。

奧創系統科技不僅是設備供應商,更是能與客戶共同成長、持續創造雙贏的工程夥伴,以卓越的解決方案,驅動產業的創新力量。

參考資料

- Closing The Test And Metrology Gap In 3D-IC Packages

- TestConX China 2020

- Thermal Control Units|Advantest Interconnect Solutions

- 高溫工作壽命- 維基百科,自由的百科全書

- 高温工作寿命- 维基百科,自由的百科全书

- High-temperature operating life - Wikipedia

- Cut Defects, Not Yield: Outlier Detection with ML Precision - SemiWiki

- (PDF) Microelectronics Reliability: Physics-of-Failure Based Modeling and Lifetime Evaluation - ResearchGate

- Mastering HTOL for Enhanced Microelectronics Reliability - Number Analytics

- High performance active temperature control of a device under test (DUT) - ResearchGate

- Too Hot To Test - Markus Kindler: Active Thermal Control - YouTube

- Overview of Research Progress and Application Prospects of Thermal Test Chips - PMC

- T-Core Active Thermal Control System - Cohu

- HTOL Systems - Reltech Limited Independent Test Laboratory

- Advantest Expands M4841 Handler with Active Thermal Control for Faster Device Throughput and Test Times | News & Events (2023)

- Pumped Two-Phase Learning Center - Advanced Cooling Technologies

- Pumped Two-Phase - Advanced Cooling Technologies

- Experimental Study of Two-Phase Cooling to Enable Large-Scale System Computing Performance

- High Heat Flux Two-Phase Cooling in Silicon Multi-Microchannels | Request PDF

- hypercool: the waterless liquid cooling solution for ai + hpc - ZutaCore

- DIELECTRIC COLD PLATE MODULAR DATA CENTER WHITE PAPER - Open Compute Project

- Two Phase Immersion Cooling: How Does It Work? - 2CRSi

- 3D Numerical Analysis of Two-Phase Immersion Cooling for Electronic Components

- Calculation of Semiconductor Failure Rates | Renesas

- Physics of failure - Wikipedia

- Aalborg Universitet An On-line Calibration Method for TSEP-based ...

- 59285 - Debugging Accuracy Issues between the Temperature Diode and the System Monitor/XADC - Adaptive Support

- A Critical Review on the Junction Temperature Measurement of Light Emitting Diodes

- proteanTecs On-Chip Monitoring and Deep Data Analytics System - SemiWiki

- Technology | proteanTecs

- proteanTecs Launches Solution for System Production Analytics Based on Chip Telemetry

- GUC GLink™ Chip Leverages proteanTecs' Die-to-Die Interconnect Monitoring

- proteanTecs announces the results of GUC collaboration - AI-Tech

- Partners - proteanTecs

- Physics of Failure (PoF) Based Lifetime Prediction of Power Electronics at the Printed Circuit Board Level - MDPI

- (PDF) Accurate Quantitative Physics-of-Failure Approach to Integrated Circuit Reliability

- Semiconductor Reliability - AVSI

- Application-Specific Power Performance Optimizer Based on Chip Telemetry